Product Introduction

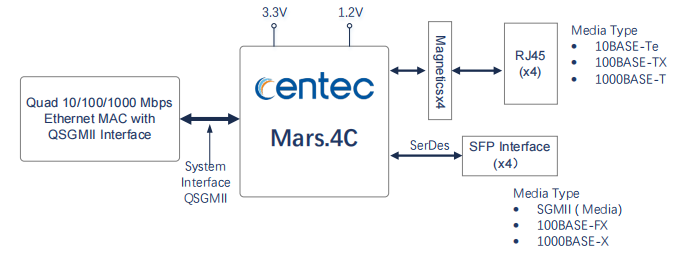

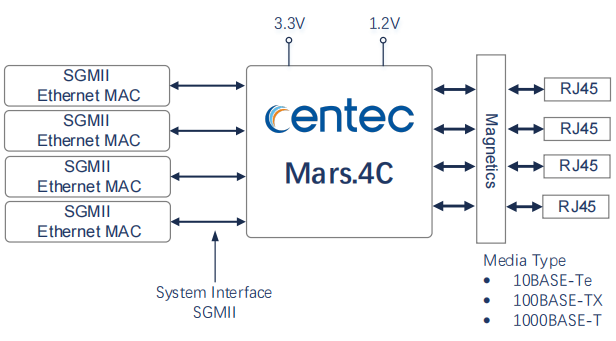

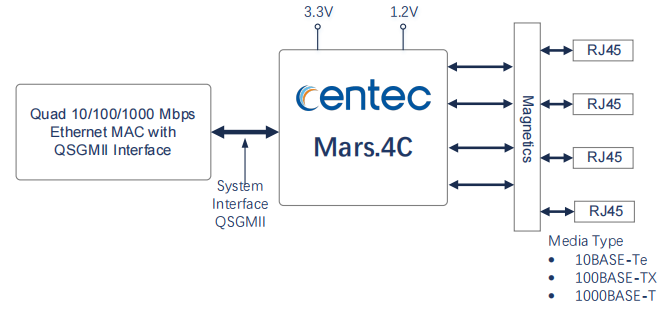

The CTC21104 integrates four independent 10/100/1000M Ethernet transceivers and four SerDes interfaces, supporting the implementation of 1000Base-T, 100Base TX, and 10Base-T Ethernet physical layer (PHY) functions on Category 5 UTP cables (excluding 1000Base-T half duplex). The 10Base Te function can also be implemented on Category 3 or 4 standard cables. The chip provides four Combo ports and can support up to four 100BASE-FX/1000BASE-X.

The chip integrates functions including PCS, PMA, and PMD sub-layers, supporting encoding/decoding, clock/data recovery, digital adaptive equalization, echo canceller, crosstalk cancellation, and line drivers, among other required circuit functions. CTC21104 also integrates an internal mixer, enabling the use of low-cost 1:1 transformer modules.

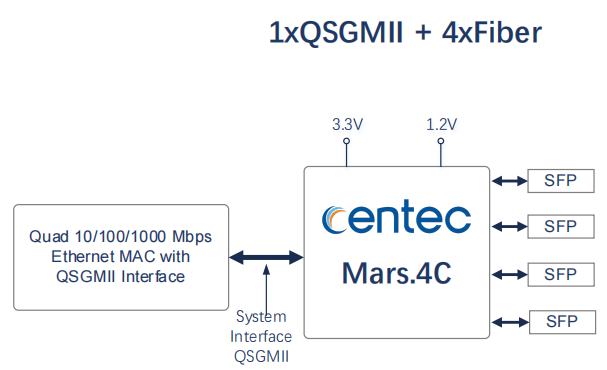

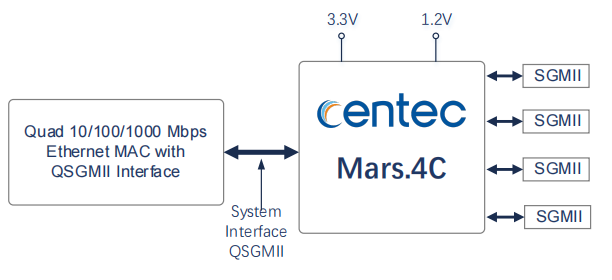

The chip supports one QSGMII output for every four independent transceivers, reducing PCB traces. All transceivers can communicate with the MAC at the same time via the same QSGMII.

Figure 1: CTC21104 (Mars. 4C) PHY chip

The chip can be flexibly configured for different operating modes:

• QSGMII x1 + Copper x 4 mode

• QSGMII x1 + Fiber x 4 mode

• QSGMII x1 + Combo x 4 mode

• QSGMII x1 + Combo x 4 mode

• QSGMII x1 + SGMII(MAC) x 4 mode

• SGMII(PHY) x4 + Copper x 4 mode

Target application

• High-density gigabit switches

• QSGMII MAC

• Copper/ Fiber Combointerface

Product Features:

• Integrated four 10/100/1000M Ethernet transceivers and four SerDes interfaces

• Support QSGMII in 10/100/1000M mode

• The physical interface supports 1000BASE-X and 100BASE-FX

• Support SGMII mode directly linked to a designated Copper GPHY for speed adaptation

• Supports IEEE 802.3az-2010 (Energy Efficient Ethernet)

– Compatible with legacy MAC or non-EEE-aware link-layer devices

• Supports cross-detection and auto-correction

• Automatic detection and correction of pair swaps, pair shifts, polarity reversals

• Supports cable detection

• Support Link Down Sleep Mode

• Support an interrupt output to an external CPU for notification

• Support quick link fault indication

• Support long-distance transmission of 120 meters @1000BASE-T

• Support serial LED interface

• Supports SyncE synchronous Ethernet clock multiplexing

– Support for recovering clocks from arbitrary SerDes

– Support clock recovery from any Copper PHY

– Support multiplexing of internal 25Mhz clock

• SerDes Test Mode

– PRBS-7/10

– IDLE/K28.5/D5.6

– User-defined

– SerDes BIST

• PHY BIST

– Support packet generation and verification

• Provides strong electromagnetic compatibility EMI/EMS, as well as good thermal performance

• Low power consumption design

• Supports 25MHz crystal and 25MHz 3.3V-OSC inputs

• Supports 3.3V and 1.2V power inputs

• Package: LQPF 176 20x20mm

Application examples