Product Introduction

CTC21108 integrates eight independent 10/100/1000M Ethernet transceivers, supporting all physical layer (PHY) functions of 1000Base-T, 100Base TX, and 10Base Te Ethernet on Category 5 UTP cables (except for 1000Base-T half duplex), and 10Base Te functions can also be implemented on Category 3 or 4 standard cables.

The chip includes PCS, PMA, and PMD sublayers that support encoding/decoding, clocking/data recovery, digital adaptive equalization, echo canceller, crosstalk cancellation, and line drivers, among other required supporting circuit functions. CTC21108 also integrates an internal mixer, enabling the use of low-cost 1:1 transformer modules.

The chip supports one QSGMII output for every four independent transceivers, reducing PCB traces.

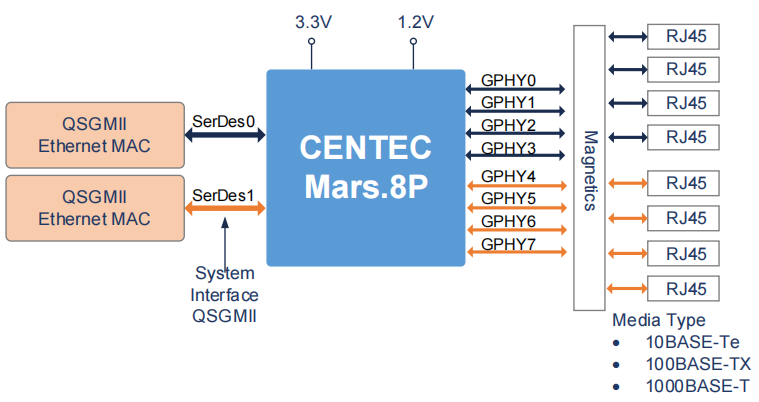

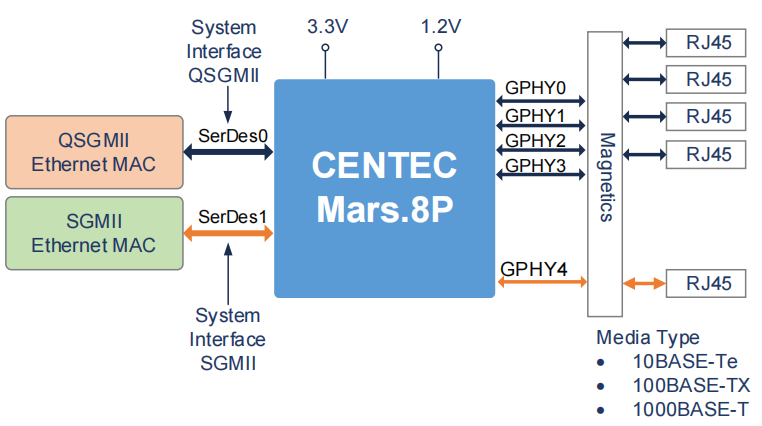

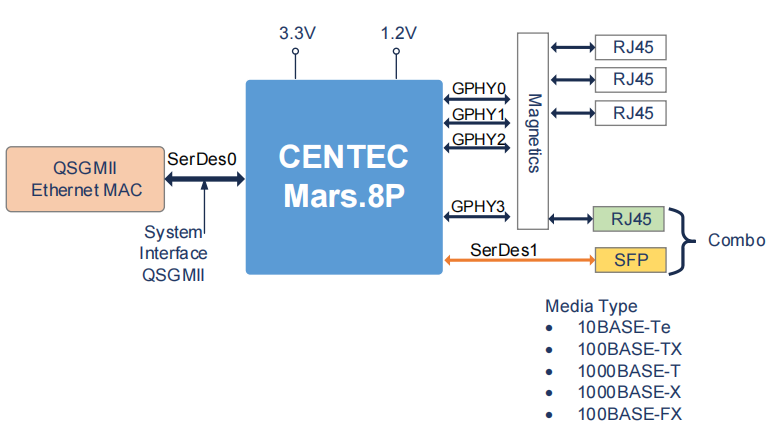

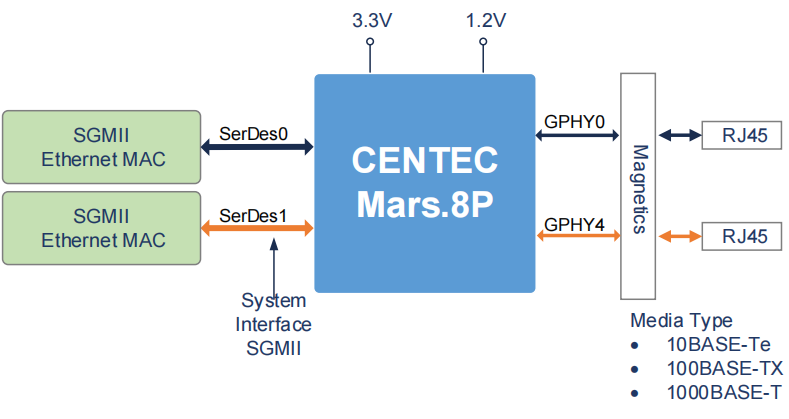

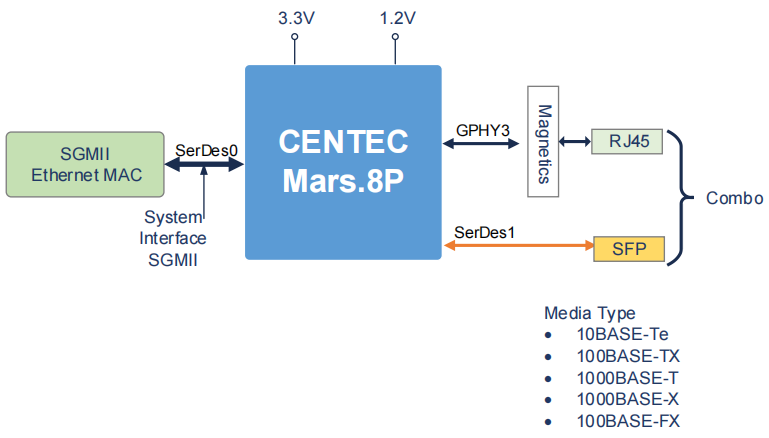

Figure 1: CTC21108 (Mars. 8P) PHY chip

The chip can be flexibly configured for different operating modes:

• QSGMII x 1 + SGMII x1 + Copper x5 mode

• SGMII x 2 + Copper x2 mode

• QSGMII x 2 + Copper x8 mode

• SGMII x 1 + Combo x1 mode

• QSGMII x 1 + Copper x3 +Combo x1 mode

Target Applications:

• High-density gigabit switches

• QSGMII MAC

Product Features:

• Each port supports full-duplex 10/100/1000M communication rate

• Support X-Range 100M long-range application function, disabled by default

– In 100M rate mode, the extension supports up to 400m cable transmission

• Support QSGMII (Quad Serial Gigabit Media Independent Interface) in 10/100/1000M mode

• Support SGMII mode directly linked to a specified Copper Giga PHY for speed adaptation

• Supports IEEE 802.3az Energy saving Ethernet (EEE)

– Support for EEE caching

– Compatible with legacy MAC or non-EEE-aware link-layer devices

•Supports Sync-E (Synchronous Ethernet)

• Cross-detection and auto-correction

• Automatic detection and correction of pair swaps, pair shifts, polarity reversals

• Support cable diagnostics

• Support an interrupt output to an external CPU for notification

• Support quick link fault indication

• Support serial LED interface

• SerDes Test Mode

– PRBS-7/10/31

– IDLE/K28.5/D5.6

– User-defined

– SerDes BIST

• Packet generation and verification are supported

• Low chip power consumption

• Easy layout, good EMI and good thermal performance

• Supports 25MHz crystal or 3.3V OSC input

• Supports 3.3V and 1.2V power inputs

• LQPF 128 package

Application examples